## **Probabilistic Circuit Fault Emulation**

David May, Walter Stechele Institute for Integrated Systems, Technische Universität München david.may@tum.de, walter.stechele@tum.de

The susceptibility of integrated circuits to soft-errors has been drastically increasing during the last decades. Transistor scaling into the nanometer regime, as well as the high demand for low-power and high-speed applications are the main reasons for this effect. Instead of trying to avoid the appearance of errors at all within the circuit with the help of costly redundancy and error-correction mechanisms, recent research is going into a different direction. By tolerating a certain error probability within the circuit it could profit from a reduced power consumption, higher operation frequency, smaller area requirement or even a combination of these [1,2]. Applications that would likely benefit from such an approach can be found in the signal processing regime, as in these applications errors might be tolerated or even unnoticed by the user. However, even there a comprehensive analysis of the circuit has to be done in advance in order to detect where in the circuit reliability requirements can be relaxed and to what extend.

We developed a probability-aware FPGA-based circuit fault emulator that helps us to answer these very same questions [3, 4]. It allows us to inject errors into the registers of any circuit based on probabilities. During run-time we can observe the outputs of the circuit and determine the output error probabilities. At the demo session we are demonstrating the emulator and the corresponding algorithms in the context of a realtime H.264 decoder. We are injecting errors at run-time into the decoder so that the effects can be seen immediately on the display. Thereby, we want to demonstrate why a careful determination of the circuits probabilistic behavior is necessary. The demo is showing how a relaxation of reliability constraints at registers not qualified for such an approach leads to an unwanted behavior. And we are showing, that when relaxed at

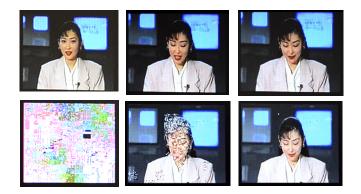

Figure 1: Dependent on the location where errors appear inside the circuit the visual quality of the decoded video is affected differently

registers that have been determined with our emulator, errors with a relatively high probability may appear, without drastically affecting the quality of the decoded video, as shown in Figure 1.

Further informations: https://lis.ei.tum.de/projects/faultify

## References

- [1] G. Anthes, "Inexact design: Beyond fault-tolerance," Commun. ACM, vol. 56, pp. 18–20, Apr. 2013.

- [2] K. Palem and A. Lingamneni, "Ten years of building broken chips: The physics and engineering of inexact computing," ACM Trans. Embed. Comput. Syst., vol. 12, pp. 87:1–87:23, May 2013.

- [3] D. May and W. Stechele, "An fpga-based probability-aware fault simulator," in *Embedded Computer Systems* (SAMOS), 2012 International Conference on, pp. 302 –309, july 2012.

- [4] D. May and W. Stechele, "A resource-efficient probabilistic fault simulator," in Field Programmable Logic and Applications (FPL), 2013 23rd International Conference on, pp. 1–4, 2013.