# **AIDA: Analog Integrated Circuit Design Automation**

Nuno Lourenço, Ricardo Martins, Ricardo Póvoa, António Canelas, Pedro Ventura and Nuno Horta Instituto de Telecomunicações, Instituto Superior Técnico, University of Lisbon

# support@aidasoft.com | www.AIDAsoft.com

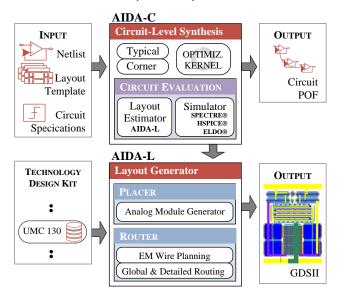

is an analog integrated circuit design automation AIDA is an analog integrated encourted in modules: AIDA-C and AIDA-L. AIDA-C is a circuit-level synthesis tool supported by state-of-the-art multi-objective optimization kernels, where the robustness of the solutions is attained by considering extreme process variations by means of PVT corner analysis. The circuit's performance is measured using Spectre®, Eldo® or HSPICE® electrical simulators. AIDA-L considers the obtained device sizes to generate the complete layout by placing and, routing the devices, while fulfilling the technology design rules by using built-in DRC and LVS procedures, taking into account the circuit's currents to mitigate electromigration and IR-drop effects. The framework also includes a technology-independent module generator, capable of creating several simple and complex device structures/layout styles that allow the AIDA-C floorplan-aware optimizer to explore a much wider space of solutions and to produce higher quality layouts. AIDA is demonstrated for different classes of circuits, such as, OpAmps, LNAs, LC-VCOs, etc. for both circuit and layout level synthesis.

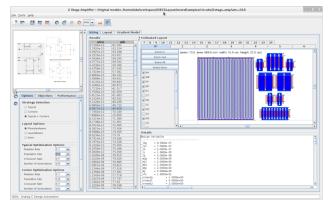

#### **Graphical User Interface**

**AIDA** includes an intuitive GUI for managing the implemented design flow with inputs and outputs from/to major commercial IC design tool sets.

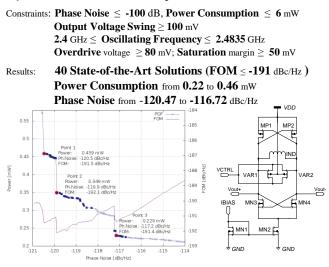

# 2.4 GHz LC-VCO

## Multi-Objective Multi-Constraint Circuit-Level Synthesis

Objectives: minimize Power Consumption and Phase Noise

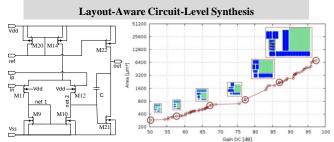

## Two-stage OpAmp

Objectives: **min. area** and **max. dc gain** Multiple Layout Templates

nct 4 4.75 D M21 **P1 C1** M9 M10 ..... л11 M12 мэс P1 **C1** M22 M22 a1 a2 M22 M22 b2 M20 b1 P2 M11 M12 **P3** М9 b м9 M10